Low‐power, high‐speed dual modulus prescalers based on branch‐merged true single‐phase clocked scheme - Jia - 2015 - Electronics Letters - Wiley Online Library

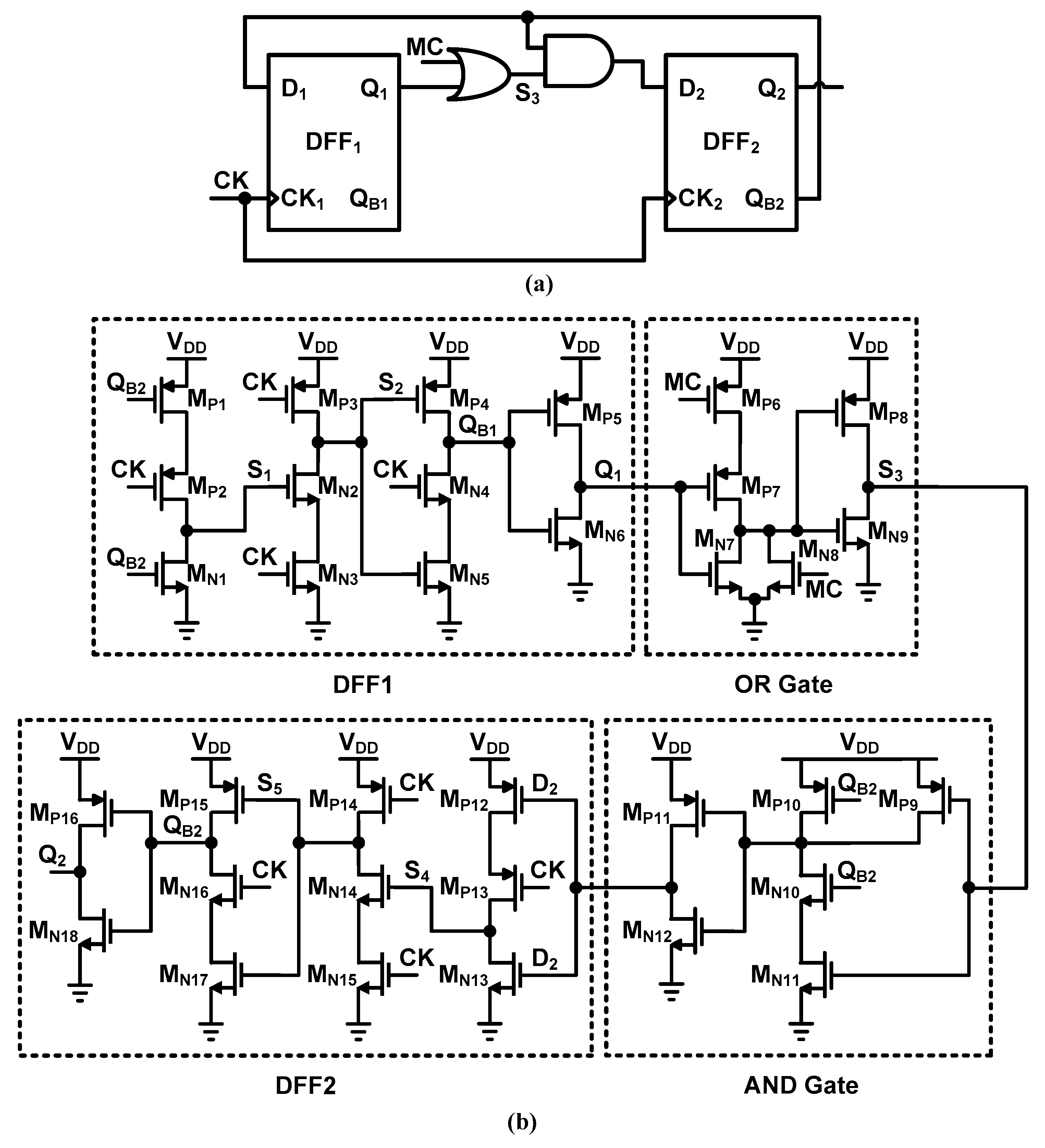

Figure 3 from A New Dynamic Floating Input D Flip-Flop (DFIDFF) for High Speed and Ultra Low Voltage Divided-by 4/5 Prescaler | Semantic Scholar

High speed and low power preset-able modified TSPC D flip-flop design and performance comparison - YouTube

![PDF] High speed and low power preset-able modified TSPC D flip-flop design and performance comparison with TSPC D flip-flop | Semantic Scholar PDF] High speed and low power preset-able modified TSPC D flip-flop design and performance comparison with TSPC D flip-flop | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/9cb813f60a762795558e9d5621efc8afd6363d35/2-Figure2-1.png)

PDF] High speed and low power preset-able modified TSPC D flip-flop design and performance comparison with TSPC D flip-flop | Semantic Scholar

Figure 2 from A NOVEL DESIGN OF COUNTER USING TSPC D FLIP-FLOP FOR HIGH PERFORMANCE AND LOW POWER VLSI DESIGN APPLICATIONS USING 45 NM CMOS TECHNOLOGY Ms . | Semantic Scholar

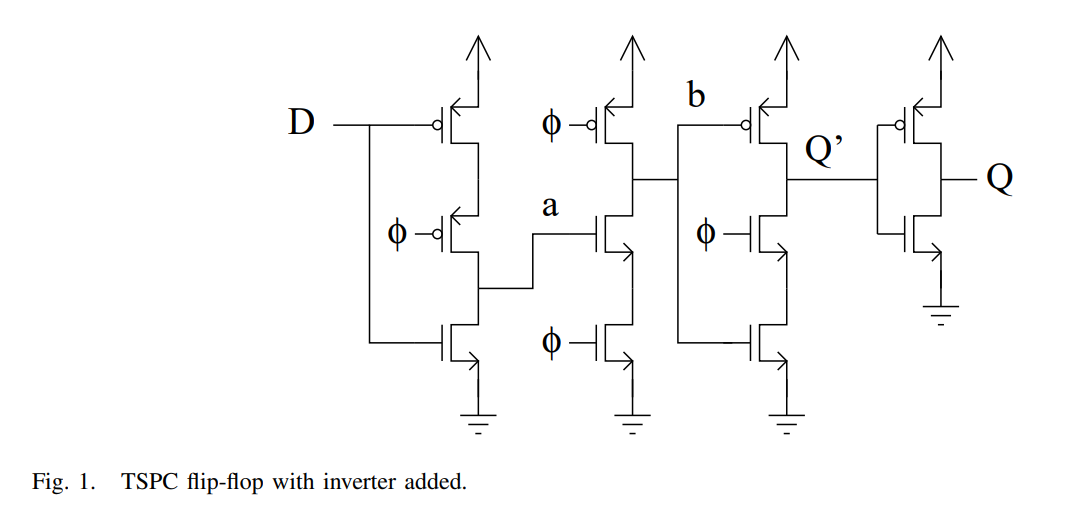

Figure 2 from A 0.4V 0.5fJ/cycle TSPC Flip-Flop in 65nm LP CMOS with Retention Mode Controlled by Clock-Gating Cells | Semantic Scholar

Configuration of TSPC D flip-flops (D-FF) for the asynchronous circuit.... | Download Scientific Diagram